近年注目を浴びている2nmプロセス。

IBMとラピダスがパートナーシップを締結したことで、国内でも話題になりました。

しかし、新技術かつ専門的な内容で理解が難しいジャンルでもあります。

そこで今回は、半導体分野の知見を多く持つ菅製作所が、2nmプロセスについてわかりやすく解説します。

現状の課題や今後の展望についても解説しますので、新技術に興味をお持ちの方はぜひご覧ください。

目次

2nmプロセスとは何か?

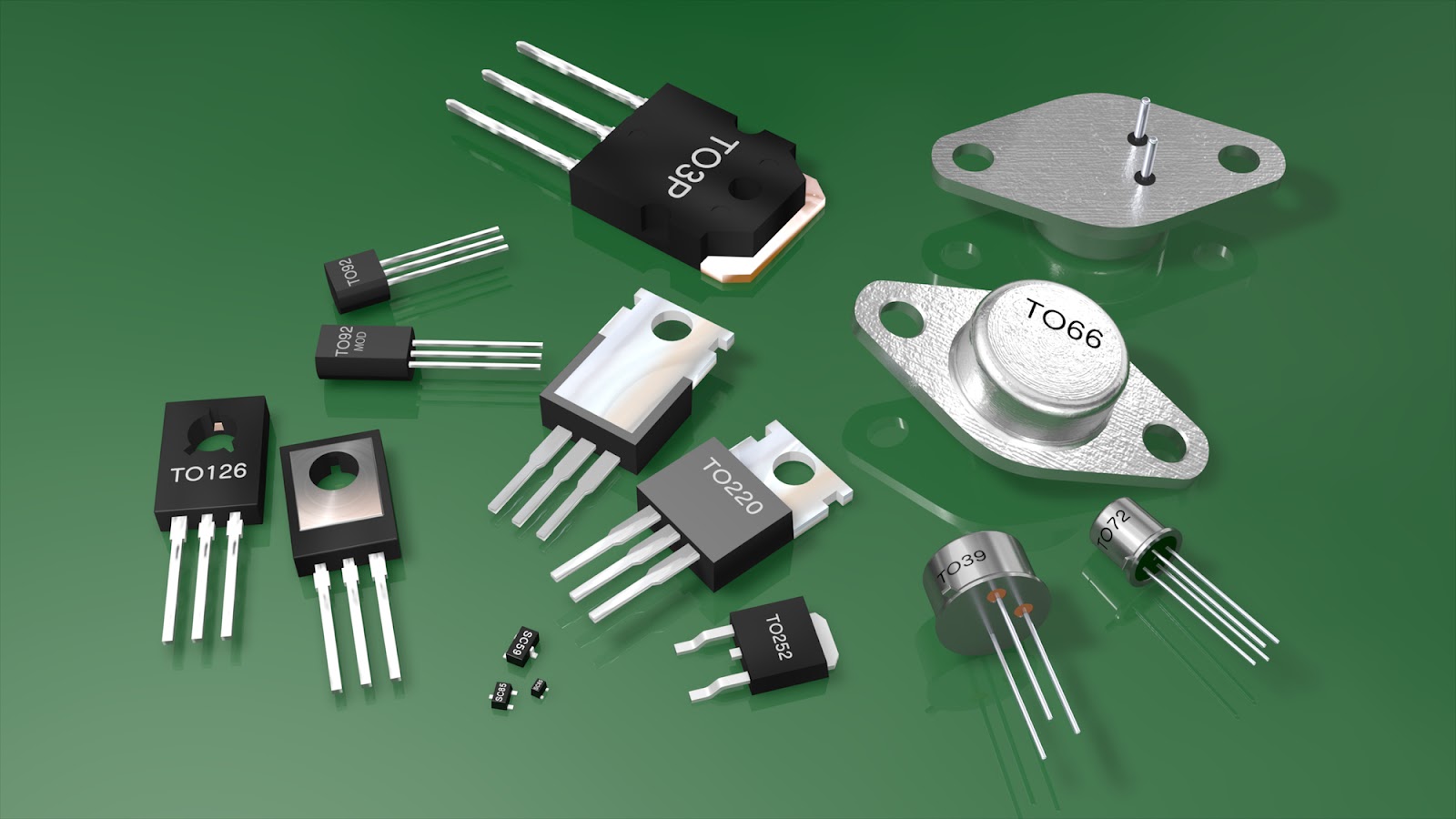

2nmプロセスは、主にトランジスタの作成に使用されています。簡単に言えば、従来よりも小型かつ高性能なトランジスタを作成するための方法です。

高性能なトランジスタはより高性能なコンピュータを作成する鍵となりますので、世界的に注力されている分野です。

2nmプロセスについて掘り下げる前に、ざっくりとトランジスタの変遷を見ておきましょう。

トランジスタの変遷

従来はプレーナー型と呼ばれる形のトランジスタを作成していました。これは、電流の切替をするためにゲートの長さを極限まで短くすることで性能向上を図っていたものです。

しかし、ゲートの長さにも限界が来てしまい、少し前のプロセスではFinFET型と呼ばれるトランジスタに移行しています。

そしてそのFinFET型にも限界が来てしまったことから、2nmプロセスではGAA FET型のものに移行しつつあるのが現状です。

簡単に言うと、今までのトランジスタでは物理的な限界が来て、より高性能なトランジスタを作るためのプロセスを開発したということになります。

2nmプロセスはトランジスタに技術革新をもたらした

ここでは、2nmプロセスの何が凄いのかを見ていきましょう。具体的には、トランジスタの分野で大きな変化がありました。

全周ゲートトランジスタ(GAA FET)の導入

GAA FETは10年に1度の技術革新と言われるほどの発明です。

GAA FETが完成すれば、従来の設計よりも性能と効率を大幅に上昇させた上で、消費電力を減らすという夢のような効果が期待されています。

トランジスタの性能が上がるということは、演算能力が飛躍的に向上するということ。小型化されたかつ高性能のトランジスタを搭載することで、コストを抑えながらデバイスの性能を向上させることができます。

ファブリケーションプロセスの詳細

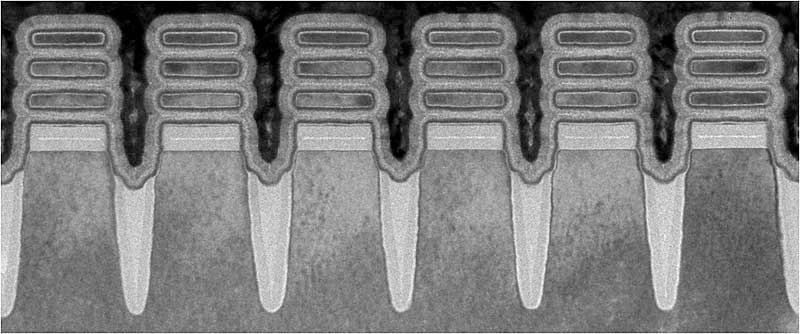

従来の方法では、チャネルを囲むゲートが3方向であり、ゲートから一部の電気がすり抜けてしまうゲートリーク電流が起きていました。

これは、量子トンネル効果によるもので、回路の誤作動の原因となり多くの技術者を悩ませたものです。

GAA FETではチャネルの4方向全てをゲートで囲むことにより、リーク電流を抑える方法が取られています。

当初は細いチューブのような「ナノワイヤー」のチャネルが使用されていましたが、現在はより多くの電流を流せる「ナノシート」のチャネルが使用されています。

2nmプロセスと次世代テクノロジー

では、2nmプロセスを活用するとどういったテクノロジーに繋がるのかを見ていきましょう。

人工知能(AI)への影響

IBMの発表によると、2012年の32nm時代では、人間一人分のニューラルネットワークを用意するには、東京ドーム1.8個分のスペース、原子炉2基程度の電力を必要とします。

これに比べ、2nmになると一般的なデータセンターのスペース、海上風力発電2基分程度の電力で運用可能とのこと。

実生活での利用では、人間一人分の性能が不必要な場合がほとんどですので、より省スペース・省電力で導入可能になります。

そのため、ビル1つに1AIというのも夢では無く、より特化したAIのサポートを受けられる可能性もあります。

より詳しい内容については、以下のページで公開されている動画でご視聴いただけます。

【対談】 “2nmプロセスって何がすごいの? AIってもっと賢くなるの かしら?“に答えます – IBM Community Japan

サスティナビリティとの親和性が高い

2nmの技術は、サスティナビリティとの親和性が高い技術でもあります。

省電力が減ることからCO2排出が減ることはもちろんですが、特に注目すべきはその演算能力の高さです。

先ほどお伝えした通り、非常に高度な演算を従来よりも少ないスペースで行うことができます。

その演算能力は、仮想空間を作り上げてその空間上で実験ができるほど。例えばサプライチェーンを仮想空間で再現することで、どのプロセスをどう効率化すれば、現実世界で効果を得られるかという実験を行えます。

複雑な問題が絡み合う課題をシミュレートを行えるようになるため、持続可能な社会を形成するために効果的な取り組みを発案できる可能性が高まります。

未来のデバイスに期待される変化

IBMによると2nmまでチップを微細化できると性能は45%上昇、消費電力は75%低下するという見積もりを発表しています。

まだ開発段階で、実際の値ではありませんが携帯電話のバッテリ寿命が4倍近くなる、データセンターからのCO2排出が激減するなど日常生活や環境問題にもメリットをもたらしてくれます。

2nmプロセスの課題

2nmプロセスには課題もあります。技術的な課題はもちろん、市場における課題や量産体制の課題もあるため一つひとつ見ていきましょう。

技術的な課題

GAA FET型の説明で、ナノシートを4方向からゲートで囲みリーク電流を抑えるという説明をしました。

机上での説明は簡単ですが、10〜20nmのシートを10nm間隔程度で積み重ね電流を流す必要があります。これには今までの技術以上に精密な制御が必要になります。

ゲートの絶縁膜が薄く、シート同士の距離も近いことからかけられる電圧も小さくなります。チップに必要な電圧とバランスが取れなければ、そもそも機能しない、トランジスタが破壊されることになります。

そのため、FinFET型のトランジスタと両立して同チップ上に搭載するなどの工夫が必要になるわけです。

新技術であるが故に、技術的な課題は山積みであることが予想されます。

ターゲットとなるアプリケーションが不明確

トランジスタに使用することで、多くの製品の向上を図れる2nmプロセスですが、現状ではどのような分野にどれだけ効果的に力を発揮するかが不明確です。

ターゲットが不明確ということは、採算の見通しも立たないということ。設備や開発の継続には維持費が必要であるため、ビジネス的にシビアな問題になります。

技術的な遅れが量産体制の遅延を招く可能性がある

日本は半導体分野において、海外と比べ10年近い技術の遅れがあります。具体的には、FinFET型の量産ができず、ひと世代飛ばしてGAA FETの開発に取り組むことになります。

構造そのものが大きく変わるため、不可能ではありませんがGAA FETではFinFETでのプロセスの多くが再利用されることから、量産体制確立までの期間が他国より長く必要になる可能性があります。

IBMとラピダスがパートナーシップを締結し、大きな一歩を踏み出し始めましたが、IBMのプロセスも量産適用されておらず、開発はできるが量産の課題が残っているのが現状です。

まとめ

近年注目を浴びている新技術、2nmプロセス。

主にトランジスタの開発に使用され、従来よりも小型かつ高性能なトランジスタを作成することにより、より高性能なコンピュータを開発できます。

そのコンピュータはAIをより身近なものにし、環境問題のシミュレートやデバイスの寿命を伸ばすなどまさに未来のテクノロジーとなる鍵になるでしょう。

しかし、技術的な問題や日本における課題がまだまだあるのが現状です。今後も2nm技術に関するニュースからは目が離せません。

菅製作所では半導体分野などのニュースや解説を記事としてわかりやすく伝えています。技術革新の波に飲まれないためにも、新しい情報をぜひご覧ください。

関連記事

参考サイト

https://notebookpc.jp/archives/6438

https://www.semiconportal.com/archive/editorial/technology/process/210507-ibm2nm.html

https://trs-ch.blog/post-4763/

https://www.odt.co.jp/trends/20230403/

https://texal.jp/2022/06/20/what-is-gaa-fet-the-most-important-technology-for-next-generation-semiconductors/

https://news.mynavi.jp/techplus/article/20221228-2548260/

https://community.ibm.com/community/user/japan/viewdocument/2nm-ai?CommunityKey=4a8dd069-484f-4fec-bb5e-1da713015c48&tab=librarydocuments

https://jp.newsroom.ibm.com/2021-05-07-IBM-unveils-worlds-first-2-nm-chip-technology-pioneering-unknown-territory-in-semiconductors