半導体製造の前工程における「電極形成」は、トランジスタなどの素子と外部回路を電気的につなぐ役割を担います。

いわば半導体内部の「電気の通り道」となる工程ですが、近年は回路の微細化と高集積化が進み、十数層に及ぶ多層配線が主流となりました。

そこで活躍するのが、銅メッキとCMPを組み合わせたダマシン法です。

本記事では、電極形成の基本的な流れから、多層配線を支える代表的な工法、成膜技術の違いまでを、初学者にもわかりやすく解説します。

長年の経験と独自の技術で、大学や研究機関での導入実績も多数。

研究目的に応じたカスタマイズや、導入前のテスト成膜も可能です。

装置のご検討やその他ご相談は、ぜひ当社までお問い合わせください。

お問合せはこちら半導体技術に関心をお持ちの皆様に、基礎から学べる情報をお届けしたいという思いから、本連載を開始いたしました。

「これから半導体について学びたい」「技術の背景を理解したい」とお考えの方に向けて、できる限り平易で役立つ内容を発信してまいります。

当社「菅製作所」は、研究開発用途の真空装置を製造・販売しております。

現場で培ってきた知見をもとに、皆様の学びに少しでも貢献できれば幸いです。

本連載が、半導体に関する疑問の解消や、さらなる理解への一助となることを願っております。

ぜひ最後までご覧ください。

目次

半導体製造・前工程における電極形成とは?

半導体製造の前工程における「電極形成」とは、ウエハー上に形成したトランジスタやダイオードなどの素子を、外部回路と電気的につなぐための金属配線や電極パッドを作る工程です。

電極は、半導体内部を流れる電気の「通り道」となる重要な役割を担っています。

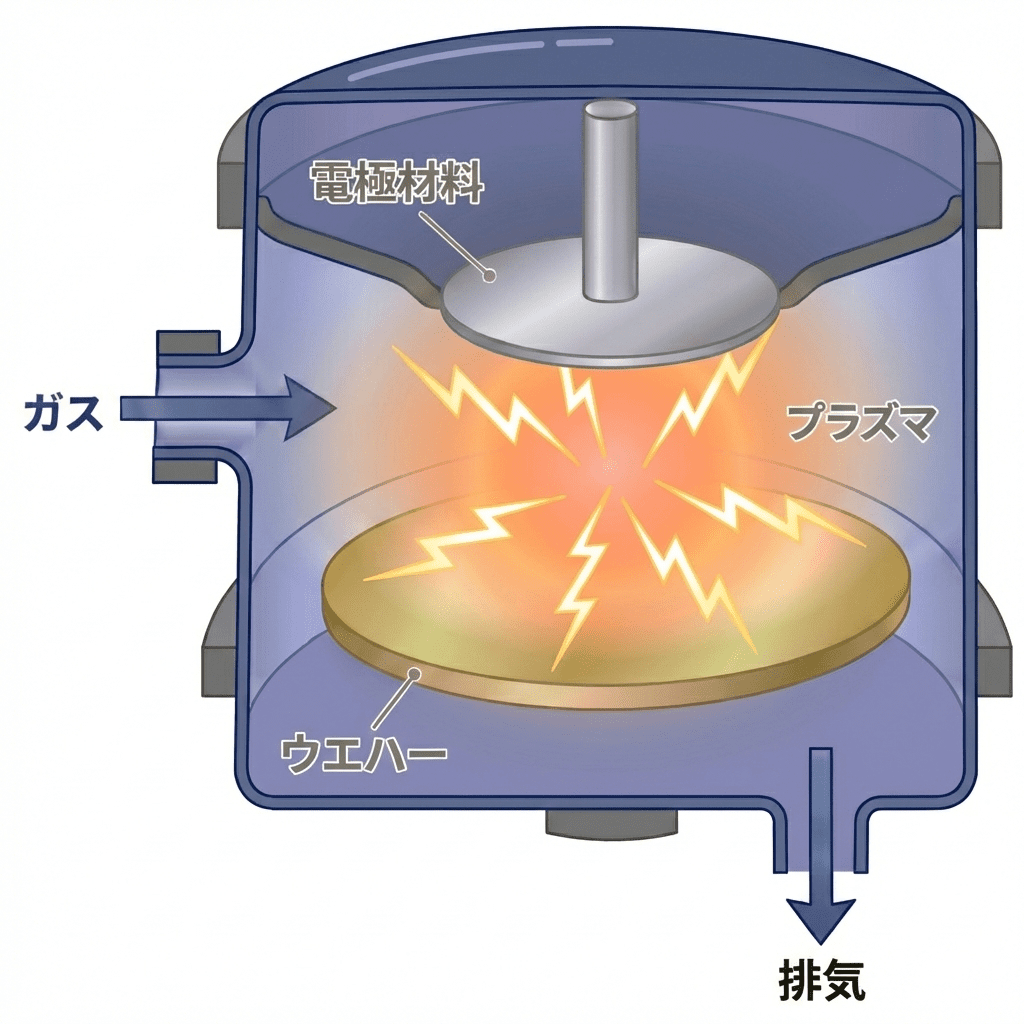

一般的には、金属材料にプラズマを照射して金属原子を飛ばし、ウエハー表面に堆積させることで金属膜を形成します。

その後、フォトリソグラフィーやエッチングを行い、必要な形状の配線へと加工します。

電極形成の精度は、デバイス性能や信頼性を左右する重要なポイントです。

電極形成|一層配線の流れ

ここでは、電極形成における「一層配線」の基本的な流れを解説します。

一層配線は、素子と最初の金属配線を電気的につなぐ重要な工程です。

各工程が正確に行われることで、安定した電気特性と高い信頼性が確保されます。

層間絶縁膜の成膜

まずはCVD法を用いて、層間絶縁膜を成膜します。

層間絶縁膜は、デバイスと配線の間、または多層配線同士を電気的に絶縁するための膜です。

一般的には酸化膜が用いられ、条件によってはボロン(B)やリン(P)を添加したBPSG膜が使われることもあります。

コンタクトホールの形成

次に、電気の通り道を確保するため、層間絶縁膜にコンタクトホールと呼ばれる開口部を形成します。

この開口によって、下層の素子と上層の配線が電気的に接続されます。

位置や寸法の精度が、その後の配線品質を左右します。

配線材料の成膜

コンタクトホール形成後、スパッタリング法によって配線材料となる金属膜を成膜します。配線には、アルミニウムや銅が用いられます。

膜質のばらつきは配線抵抗や信頼性に影響を与えてしまうため、ウエハー全面に均一な金属膜を形成することが重要です。

配線パターンの形成

金属膜が形成されたら、フォトリソグラフィーによる露光・現像を行い、エッチングによって不要な金属を除去します。

こうして設計どおりの配線パターンが作られますが、微細化が進むほど、この工程の精度管理が重要になります。

保護膜の形成

最後に、湿気や汚染物質からデバイスを守るための保護膜を形成します。

その後、電極パッド部分をパターニングして保護膜を除去し、外部接続が可能な状態に仕上げます。

ここまでが、一層配線における電極形成の一連の流れです。

実はあまり使われていない「一層配線」

実際の半導体製造では、一層配線が使われるケースはほとんどありません。

回路の高集積化が進んだ先端ロジック半導体では、配線本数が大幅に増えるため、十数層にも及ぶ多層配線構造が一般的になっています。

多層配線を採用することで、限られたウエハー面積でも複雑な回路設計が可能となり、高性能かつ高機能な半導体デバイスの実現につながります。

次章では、多層配線で使われる「ダマシン法」について解説します。

多層配線で使われる「ダマシン法」とは?

ダマシン法とは、銅メッキとCMP(化学機械研磨)を組み合わせて配線を形成する技術です。

近年、半導体の微細化が進むにつれて配線は細くなり、電気抵抗の増大が課題となってきました。

その対策として、従来のアルミニウムに代わり、低抵抗で信頼性にも優れた銅が配線材料として使われています。

ただし、銅はエッチング加工が難しいという特性があります。

そこで、層間絶縁膜にビアと呼ばれる配線用の穴を形成し、そこへ銅を埋め込み、CMPで表面を平坦化します。

この手法がダマシン法であり、十数層にも及ぶ多層配線を可能にしているのです。

電極形成に使用される成膜技術

電極形成では、用途や膜質に応じて複数の成膜技術が使い分けられています。

ここでは、代表的な成膜手法であるスパッタリング法とCVD法について解説します。

スパッタリング法

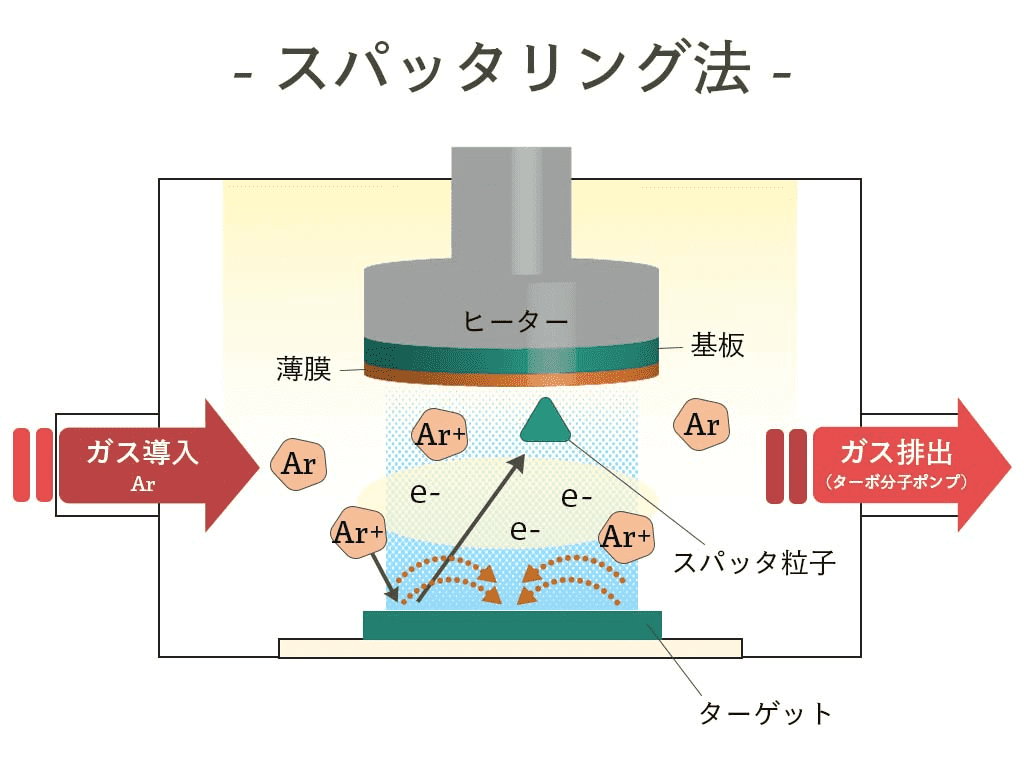

スパッタリング法は、真空中でアルゴンなどのガスをプラズマ化し、そのイオンをターゲット(金属材料)に衝突させて原子を弾き出し、ウエハー表面に堆積させる物理的成膜技術です。

半導体の電極形成では、AlやCu系配線をはじめ、Ti/TiNなどのバリアメタル、透明電極の成膜にも用いられます。

膜厚の均一性や組成再現性に優れており、高融点金属や合金にも適用できる点が大きな特長です。

CVD法(化学気相成長法)

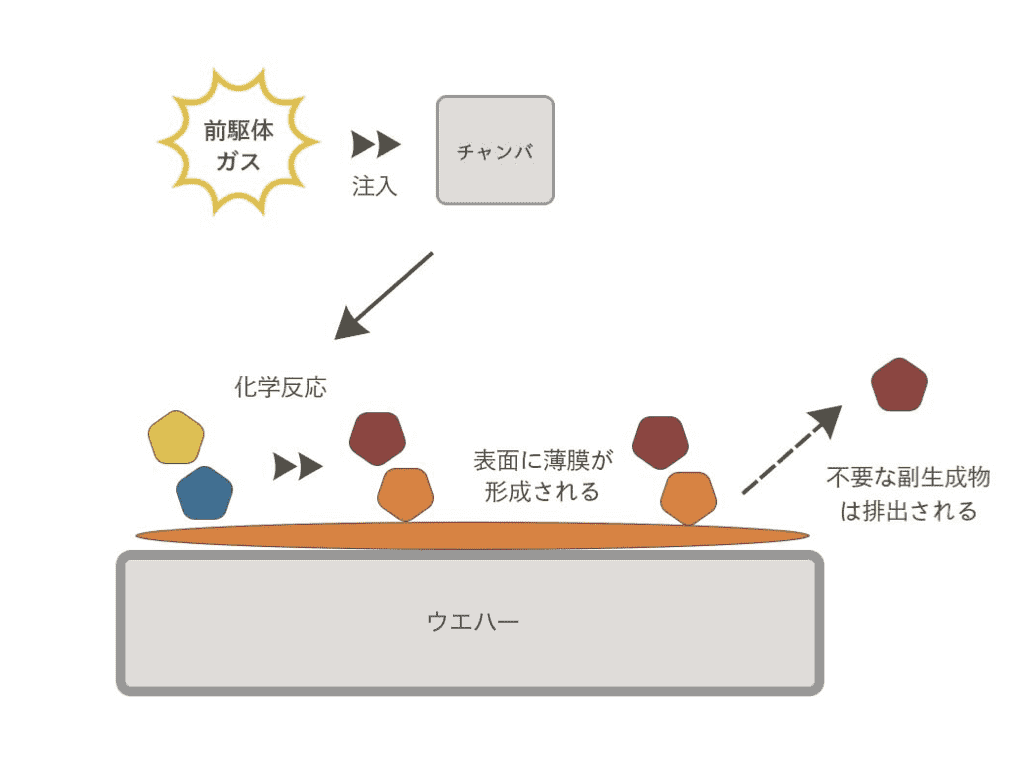

CVD法は、原料ガスをウエハー表面に供給し、化学反応によって薄膜を形成する成膜技術です。

基板上で原料ガスが分解され、蒸気圧の低い物質へ変化することで、再蒸発しにくい薄膜として堆積します。

生成された副生成物は排気されるため、安定した膜形成が可能です。

CVDは電極形成だけでなく、電子デバイスや各種コーティング分野でも広く活用されています。

まとめ

電極形成は、半導体内部に電気の通り道を作り、デバイスとして機能させるために欠かせない工程です。

一層配線を基本として理解しつつ、実際の製造では多層配線やダマシン法が用いられ、高集積・高性能化が実現されていることをご理解いただけましたでしょうか。

スパッタリングやCVDといった成膜技術を適切に使い分けることで、微細で信頼性の高い配線形成が可能になります。

長年の経験と独自の技術で、大学や研究機関での導入実績も多数。

研究目的に応じたカスタマイズや、導入前のテスト成膜も可能です。

装置のご検討やその他ご相談は、ぜひ当社までお問い合わせください。

【参考文献】

今と未来がわかる半導体(ナツメ社)

図解入門 よくわかる最新半導体の基本と仕組み(秀和システム新社)